LimeSDR-QPCIe Implementation

Note

The LimeADPD algorithm is implemented via the LimeSDR-QPCIe board

LimeSDR-QPCIe incorporates two LMS7002M transceiver chips, designated LMS1 and LMS2. The board is dedicated to 4G LTE signal transmission.

LimeADPD is implemented in LMS1 transmit path.

Two TX channels, designated A and B, are implemented by LMS1. Only one LMS1 receive path is used to implement both DPD monitoring paths.

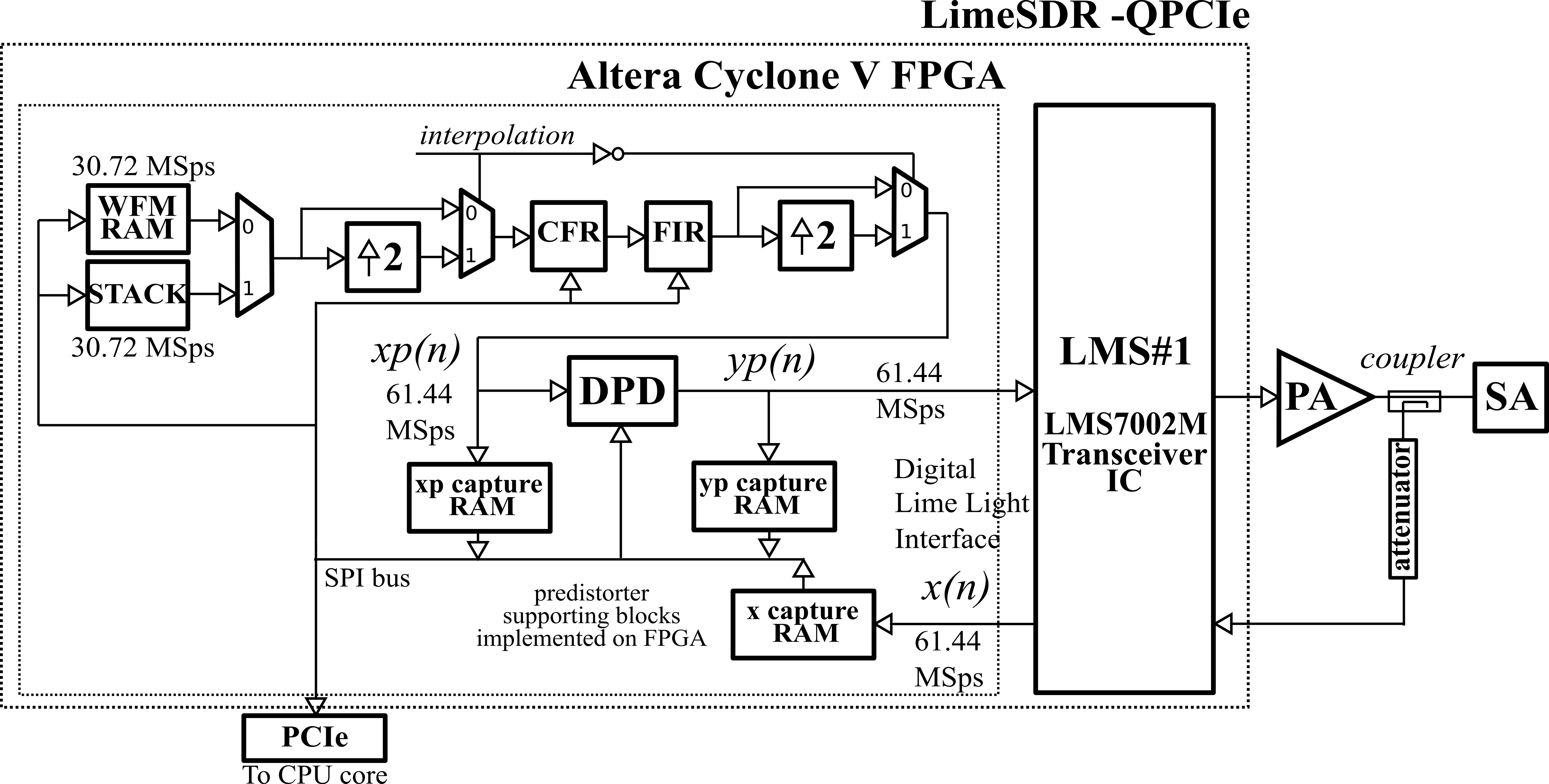

ADPD and CFR algorithms are implemented using LimeSDR-QPCIe board, a high level block diagram of which is shown in Figure 10.

The LimeSDR-QPCIe board has many more options than shown, e.g. two LMS7002M chips, USB interface and GPS receiver etc. LMS7002M itself is a 2T-2R RF IC. For clarity, the figure shows the minimum hardware options required to illustrate the LimeADPD implementation. The same signal names used in Figure 1 are used here.

DPD operates at 122.88 MHz clock, while its input/output sample rates are 61.44 MS/s. An interpolation block is used to double usual LTE sample rate of 30.72 MS/s before driving DPD block. A DPD sample rate of 61.44 MS/s (or higher) is required if we want to cancel at least IMD3 products in case of 20 MHz modulation.

Figure 10: ADPD implementation based on LimeSDR-QPCIe board.

As shown in Figure 10, frequency conversion from BB to RF is performed by LMS7002M transmitter chains. Frequency down-conversion from RF to BB is implemented by only one LMS7002M receive chain dedicated to ADPD, i.e. one receiver of the available RF RX chains is allocated as ADPD monitoring path. In the case of MIMO applications, the same ADPD monitoring path is used as a time-sharing resource to linearize multiple PAs, which saves power consumption as well as on board RF resources.

The pre-distorter, external ADCs and DACs operate at rate of 61.44 MHz. Regarding data converters, LMS7002M on chip 12-bit DACs and ADCs are used. The data rate at the LimeLight interface is 61.44 MS/s.

In order to increase the capacity of the radio link, a 2x2 MIMO transceiver is implemented. One transceiver IC, LMS1, is used to implement two MIMO transmitters. In each of the transmitting channels, separate DPD, CFR and low-pass FIR filter blocks are implemented. Another transceiver IC is used to implement regular MIMO receivers.

CFR block has provision of changing the number of FIR filter taps L in the range 1 ≤ L ≤ 40.

Using the same interface, clipping threshold can be set to 0 ≤ Th ≤ 1. It is floating point number. The value of 0 is equivalent to “CFR power down” while 1 corresponds to “CFR bypass”.

The interpolation/decimation option can be enabled or disabled. The choice is related to the modulation bandwidth as shown later.

CFR output is filtered by on-FPGA digital low-pass post-CFR FIR filters (Figure 10). These filters are very frequency selective and efficiently remove out-of-band unwanted products generated by BB digital modem as well as CFR PW method itself.

Two CFR blocks have been implemented for both transmitted channels. The 40-tap PWCFR module operates at 122.88 MHz clock frequency.

If the interpolation control signal is zero (see Figure 10) the data rate of CFR input signal samples (from WFM RAM) to CFR input is 30.72 MS/s. Therefore, the PWCFR operates at the clock frequency level which is 4 times greater than the processing data rate. In this case, the data interpolation (using up-conversion of factor of 2) is used after CFR and post-CFR FIR blocks (see Figure 10). The number of taps in these filters is 40. The order L is in the range 1 ≤ L ≤ 40.

If the interpolation control signal is equal to one (Figure 10), interpolation (using up-conversion of factor of 2) is used in front of CFR and post CFR FIR blocks. (see Figure 10). In this case, the data rate of signals processed by CFR and post-CFR FIR blocks is equal to 61.44 MS/s. Therefore, the PWCFR operates at the clock frequency level which is only 2 times greater than processing data rate. The data interpolation, located after the CFR and post-CFR FIR blocks, is now bypassed. The number of taps in the CFR and post-CFR low-pass filters is limited to 20. Therefore, the L is in the range 1 ≤ L ≤ 20.